V reakci na AllGah! / Elektrolab

Na serveru elektrolab.eu jsem narazila na poměrně zajímavý článek na téma univerzálního dvouvstupového jednovýstupového logického hradla:

https://www.elektrolab.eu/blog/allgah-vic-logickych-funkci-na-dvou-vstupech-nez-si-myslite

Ten článek je velice zajímavý, rozhodně ho doporučuji přečíst, ač je to s prominutím objevování kola, trojúhelníkového navíc, ale budiž, stejně je to v závěru poučné.

Návrh řešení

Systém se dvěma dvoustavovými vstupy a jedním výstupem a možností plnit libovolnou naprogramovanou úlohu není nic jiného než čtyřbitová ROM, no a protože do čtyřech bitů se vejde právě šestnáct různých čísel (2⁴), je celkem logické, že těch možných logických úloh bude též 16, na tom není co vymýšlet. Z toho bude vycházet i moje i implementace, kde potřebuji nějakou strukturu, která mi ty čtyři bity udrží. Já pro jednoduchost použiji jumpery, pak potřebuji adresní dekoder, čili něco, co mi vybere jeden z těch čtyřech bitů na výstupu podle libovolných dat na vstupu, možnosti na vstupu jsou právě čtyři: LL, LH, HL, HH, čili potřebuji převést LL na LLLH, LH na LLHL, HL na LHLL a HH na HLLL. Detekovat stav HH je jednoduché, stačí použít hradlo AND. Obdobně triviálním je i stav LL, protože inverzí LL dostanu HH a pak postupuji úplně stejně. Zbývají stavy LH a HL, kdy invertuji právě jeden ze vstupů, čili LH překlopím na HH a opět následuje AND, obdobně mohu postupovat v případě HL. Dekodovanou jednou ze čtyřech možností potom pošlu přes jumpery, přes které se buď H protlačí na výstup (zapojený jumper), nebo neprotlačí (nezapojený jumper) a výstup bude stažen do L. Výstup jumperů potom sloučím jedním velkým OR (tady tiše předpokládám statickou strukturu a současně že H>L, neboli H=1, L=0, ono to může být i jinak).

Optimalizace řešení

Výše uvedené řešení není optimální z výrobního hlediska, protože na vstupu mám dvoje různá hradla, přesněji řečeno invertor a AND, navíc v problematických počtech, v rámci logiky řady 74×× se invertory vyrábí v šesticích, kdežto dvouvstupová AND toliko v čtveřicích, navíc s problematickou dostupností. Toto nechci, je to nepraktické. Pokud bych mohla namísto AND použít NAND, pak bych mohla vyrobit invertor pomocí NAND, přesněji řečeno NAND se spojenými vstupy a mám na vstupu jeden typ IC. V tomto případě tedy budu tj. LL převádět na HHHL, LH na HHLH, HL na HLHH a HH na LHHH a potom přes jumpery budu na výstup vnucovat L namísto H a slučovat budu pomocí AND, popřípadě, pravdivostní tabulka je programovatelná libovolně, tudíž mohu slučovat přes NAND, což se projeví jako inverze výstupu a zrovna se to hodí nejen elektricky, ale též tím, že zapojením jumperu vnucují L, což se za NAND projeví jako H, čili jumper (případně sepnutý spínač) ve výsledku znamená H na výstupu, což je lidskému myšlení přirozené. Adresní dekoder mohu postavit výhradně na NAND hradlech, které jsou dostupnější. Řešení tedy nejen existuje, ale je současně dostatečně jednoduché. Říkejte mi Satane…

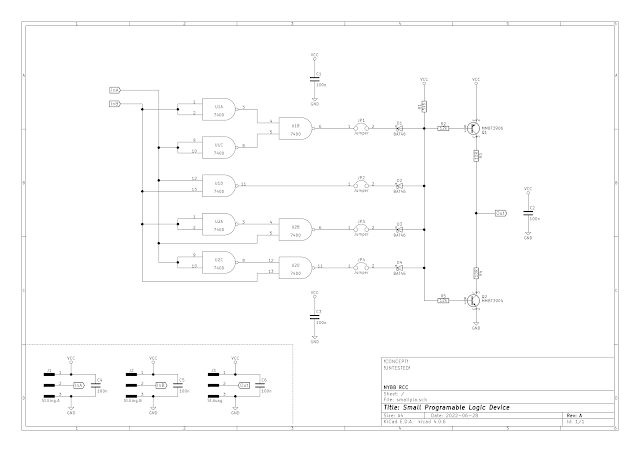

Zapojení by mělo být po předchozím textu víceméně samovysvětlující, takže jen doplním. IC1 obstarává detekci HH a LL. IC2 obstarává detekci HL a LH. Přestože by bylo možno použít signály z invertorů pro detekci LL, rozhodla jsem se použít separátní invertory, především s ohledem na návrh DPS, který by tahání velkého množství signálů mezi IC zbytečně komplikovalo. Ze stejného důvodu jsem se rozhodla použít dvě stejné čtveřice NAND, ač by bylo možné použít jednu čtveřici NAND a jednu šestici invertorů s tím, že by se z ní použily toliko dva. Už samo přiřazení sekcí obou obvodů je provedeno s ohledem na snadnost návrhu DPS.

Dostupnost dvojice čtyřvstupových NAND je problematická, navíc by to komplikovalo desku, proto jsem se rozhodla výstupní NAND navrhnout z diskrétních součástek. Současně je to dobrou ukázkou toho, jak TTL logika zevnitř vypadá a jak jí nastykovat se zbytkem světa. Návrh je optimalizován na nízký příkon, z čehož plyne i nízká rychlost, ale vzhledem k použitým hradlům na vstupu a jumperům v tom nevidím problém. Pro dosažení vyšší rychlosti by R1, R2 a R5 měly být menší, řádově, bázové proudy Q1 a Q2 by měly být kolem 1mA (což je nemálo) a potom bychom se s velkou slávou při správném návrhu desky dohrabali na zpoždění hradla kolem 50ns, což je i tak želva master level, ovšem vzhledem k těm 7400 na vstupu a jumperům to stejně nedává smysl. Velice bych se divila, kdyby se celý tento bastl dostal jako celek pod 500ns, proto jsem volila cestu menšího příkonu a pomalejšího výstupu.

Případné modifikace

Kdybych to myslela s rychlostí vážně, bylo by lepší použít na vstupech nevylučující NOR, které jsou už ze své podstaty rychlejší, následně to celé optimalizovat na úrovni hradel. Obdobně programování na jumperech není nic extra, dalo by se to udělat opět na hradlech, celé by se to dalo překlopit do diferenciální logiky atd., ostatně hrát si s ptákovinami jde opravdu hodně dlouho. V této souvislosti doporučuji kouknout na FPGA, kde je veliké množství velice podobných struktur, ovšem typicky mají čtyři vstupy, jeden výstup, takže 16bitovou konfigurační SRAM na jednu buňku.

Závěr, dodatky

Pokud jde o míchání HC, HCT, AC, ACT, LS, ALS, whatever, logiky, je potřeba si uvědomit, že to není diferenciální logika, takže každý prvek zpozdí náběžnou i sestupnou hranu, navíc to samozřejmě udělá rozdílně, jinými slovy, dokáže to hýbat s šířkou pulzu a to tak, že i dosti zásadně. To je řekněme vlastnost TTL kompatibilní logiky a cena za jednoduchost implementace. V podstatě se ty různé druhy rozpadají třemi směry — technologie (komplementární BJT, nebo OC s BJT vs CMOS), rychlost (což typicky souvisí jednak s parametry a pracovními body použitých tranzistorů) a rozhodovací úroveň a hystereze mezi H a L. HC a HCT je oboje CMOS, ale HCT má jinde rozhodovací úroveň. Jediné, co dokáže člověku namlátit u pomalých signálů je právě rozhodovací úroveň.

Pominu-li, že je to složité řešení jednoduchého problému, pak bohužel uvedená schemata jsou prakticky neanalyzovatelná, protože první, co bych s tím musela udělat, je nějak lidsky to překreslit, což je podle mého názoru přesně to místo, kde to autorovi nejvíce namlátilo. Pokud se podívám na to schema s černým pozadím (na jiné nemám odvahu, tady je alespoň vidět myšlenka na první pohled), pak na obou vstupech je XOR, což umožňuje kterýkoliv z nich invertovat. Následují XOR, AND, OR hradla, čímž se dělá logika nad vstupy. Následuje pětice AND, které vybírají jeden z pětí signálů (ničím není zaručené aby to byl právě jeden, to se tak prostě musí zkonfigurovat), tedy jeden z výstupů výše zmíněných hradel doplněný ještě o oba vstupy, což se v dalším stupni slučuje na čtveřici OR a vede do výstupního XOR, který dělá podmíněnou negaci. Je to sice krajně nepraktické řešení, ale musí fungovat. Střed pomocí AND vybere jednu z pěti operací (AND, OR, XOR, přenos prvního vstupu, přenos druhého vstupu), dále každý ze vstupu může být invertovaný, což nabízí další čtyři možnosti, čili řekněme 20 nastavení, přičemž ještě lze invertovat výstup, což přináší další dvě možnosti, čili 40 různých nastavení. Ona se některá z nich musí nevyhnutně překrývat, neb pravdivostní tabulka celku bude mít toliko čtyři řádky (máme dva vstupy), přičemž každý z řádků může na výstup poslat buď nulu, nebo jedničku. Ze čtyřech dvoustavových věcí mohu udělat nanejvýše 16 kombinací, čili těch pravdivostních tabulek je reálně 16, lépe řečeno, nemůže jich být více, tj. někde v tom plave 40-16=34 možných nastavení, tedy dá se říct, že každá funkcionalita je tam definovaná v průměru třikrát. Čímž chci primárně upozornit na to, že logické výrazy lze upravovat a současně tím lze dosáhnout poměrně zásadního zjednodušení celé úlohy.

Celkově to ale hodnotím pozitivně. Autor sice znovu vymyslel kolo, ta struktura, ke které se chtěl dostat, je základem prvních programovatelných logických polí, zjevně na to přišel sám a jak už to tak bývá, na první pokus to chytil to za špatný konec, ale ono to taky chvíli trvalo než jsme koncem 80. let došli k prvním Xilinxům. Je to jedna ze slepých uliček do kterých člověk padá běžně a které prostě musí projít, aby zjistil, že tudy cesta nevede a musí se to udolat z jiné strany. Tedy ono je to běžné pouze pokud se snaží něco vymyslet, lhala bych, kdybych tvrdila, že tohle nemám, prakticky každá věc mi namlátila a ukázala mi, že nevím něco naprosto samozřejmého, tedy samozřejmého v momentě, kdy už víte. Tento obor prostě není pro ty, co se hroutí když něco nedopadne na první pokus dobře, ale o to zajímavější to je.

Zdravím, tady ten autor. 1) Olga 2, kterou tu už ladíme na celou číslicovou techniku (4 vstupy, 2 výstupy) už tohle řeší v procáku na pár ifech 2) Ano, na projektu AllGah (Olga 1) jsem se naučil pájet a pochopil tranzistory 3) Ano, jde to optimalizovat a udělat z toho konfigurovatelného švába, stačí 4 vstupy na konfiguraci, 2 vstupy, 1 výstup, chip enable a Vcc a Gnd, tedy 10 nožiček, o to šlo 4) škoda, že nejste na facebooku, mohla by s Váma bejt celkem sranda :)

OdpovědětVymazat